Si-gate N-channel ion-implant process

Handshake bus-access control on chip

Three user-accessible control-flag outputs

Separate serial-data input and output ports

Direct interfacing to standard memory parts

Address capability to 65k bytes of memory

· Capability to interface with memories or peri-

canabilities

Simplified programming

and implied

Simpler I/O hardware

Interface flexibility

Direct control output

Two sense inputs

Simplified timing hardware

On-chip clock generator

pherals of any speed

Simplified power requirements

Large system capability

Single 5-volt supply

Low power

Plastic package

Lower cost

Direct Memory Access (DMA) and multiprocessor

Multiple addressing modes - program-counter-

relative, immediate data, indexed, auto-indexed,

# ISP-8A/600 single-chip 8-bit n-channel microprocessor (SC/MP-II)

## general description

SC/MP (Simple Cost-effective MicroProcessor) is a single-chip 8-bit microprocessor packaged in a standard, 40-pin, dual-in-line package.

N-channel, silicon gate, depletion mode standardprocess technology ensures high performance, high reliability, and high producibility.

SC/MP is intended for use in general-purpose applications where cost per function is a most significant criterion. But cost efficiency is only a part of SC/MP's story. It goes on to include a variety of useful functions that are not even provided by some of the expensive microprocessors, like self-contained timing circuitry, 16-bit (65k) addressing capability, serial or parallel data-transfer capability and common memory/ peripheral instructions. The built-in features in conjunction with the low initial cost describe what SC/MP really is - a microprocessor specifically designed to provide the simplest and most efficient solution to many application requirements.

## customer benefits

- Simpler interfacing

- Bidirectional TRI-STATE<sup>®</sup> 8-bit data bus

- TTL-compatible input/output interface

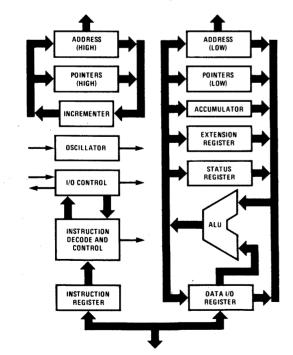

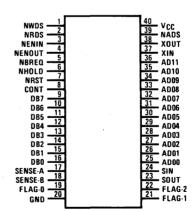

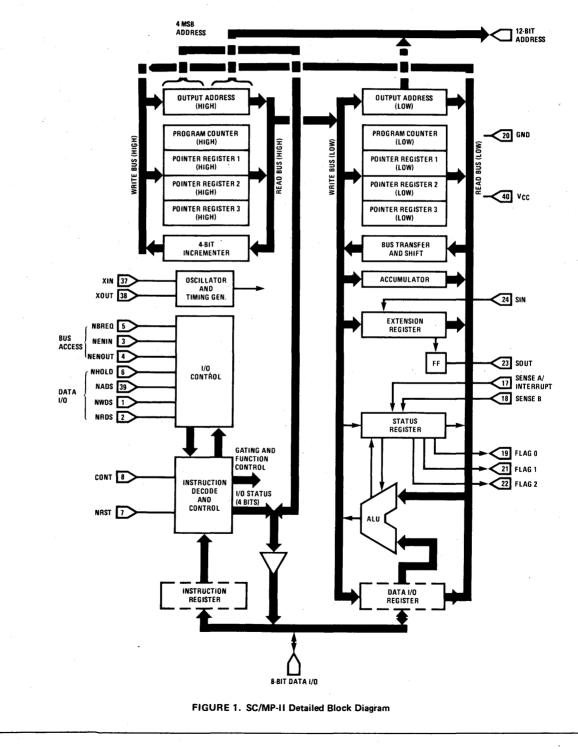

## block and connection diagrams

#### SC/MP-II Pin Configuration

SP-8A/600 single-chip 8-bit n-channel microprocessor (SC/MP-II

© 1977 National Semiconductor Corp.

DA-B20M37/Printed in U.S.A

National Semiconductor

MICROPROCESSOR

## applications

## absolute maximum ratings (Note 1)

- Test Systems and Instrumentation

- Machine Tool Control

- Small Business Machines

- Word Processing Systems

- Educational Systems

- Multiprocessor Systems

- Process Controllers

- Terminals

- Traffic Controls

- Laboratory Controllers

- Sophisticated Games

- Automotive

## dc electrical characteristics $(T_A = 0^{\circ}C \text{ to } + 70^{\circ}C, V_{CC} = +5 \text{ V} \pm 5\%)$

| Parameter                                                                | Conditions                                | Min.                | Max. | Units      |

|--------------------------------------------------------------------------|-------------------------------------------|---------------------|------|------------|

| INPUT SPECIFICATIONS                                                     | · ·                                       | · · · · ·           |      |            |

| All Input Pins Except V <sub>CC</sub> and GND<br>Logic "1" Input Voltage |                                           | 2.0                 | Vcc  | v          |

| Logic "0" Input Voltage                                                  |                                           | -0.5                | 0.8  | V          |

| Input Capacitance<br>(All pins except V <sub>CC</sub> and GND)           |                                           |                     | 10   | pF         |

| Supply Current                                                           | T <sub>A</sub> = 25°C<br>outputs unloaded |                     | 45   | mA         |

|                                                                          | T <sub>A</sub> = 0°C<br>outputs unloaded  |                     | 50   | mA         |

| OUTPUT SPECIFICATIONS                                                    |                                           |                     |      |            |

| "TRI-STATE <sup>®</sup> " Pins (NWDS, NRDS,<br>DB0 - DB7, AD00 - AD11)   |                                           |                     |      |            |

| Logic "1" Output Voltage                                                 | I <sub>OUT</sub> = -100μA                 | 2.4                 | ·    | V          |

| Logic "0" Output Voltage                                                 | IOUT = 2.0mA                              |                     | 0.4  | V          |

| NADS, FLAG 0 - 2, SOUT, NENOUT<br>Logic "1" Output Voltage               | I <sub>OUT</sub> = -100μA                 | V <sub>CC</sub> - 1 |      | V          |

| Logic "1" Output Voltage                                                 | IOUT = -1mA                               | 1.5                 |      | . <b>V</b> |

| Logic "0" Output Voltage                                                 | IOUT = 2.0mA                              |                     | 0.4  | v V        |

| NBREQ (Note 2)<br>Logic "0" Output Voltage                               | IOUT = 2.0mA                              |                     | 0.4  | v          |

| Logic "1" Output Current                                                 | 0 ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>    |                     | ±10  | μA         |

| XOUT<br>Logic "1" Output Voltage                                         | lout = -100μA                             | 2.4                 |      | v          |

| Logic "0" Output Voltage                                                 | IOUT = 1.6mA                              |                     | 0.4  | v          |

| Parameter                                                             | Conditions                                                          | Min.                             | Max.               | Units    |

|-----------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------|--------------------|----------|

| f <sub>x</sub>                                                        |                                                                     | 0.1                              | 4.0                | MHz      |

| ^                                                                     | R = $240\Omega \pm 5\%$ (figure 2B)<br>C = $300 \text{pF} \pm 10\%$ | 2.0                              | 4.0                | MHz      |

| Г <sub>С</sub> (Note 4)                                               |                                                                     | 500                              |                    | ns       |

| Microcycle                                                            |                                                                     | 1                                |                    | μs       |

| External Clock Input (see figure 2A)<br>TW0                           |                                                                     | 120                              |                    | ns       |

| Tw1                                                                   |                                                                     | 120                              |                    | ns       |

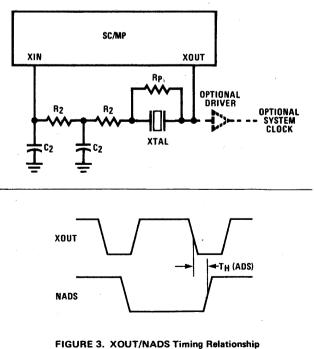

| XOUT/ADS Timing Relationship<br>(see figure 3)<br>TH (ADS)            |                                                                     | 100                              | 225                | ns       |

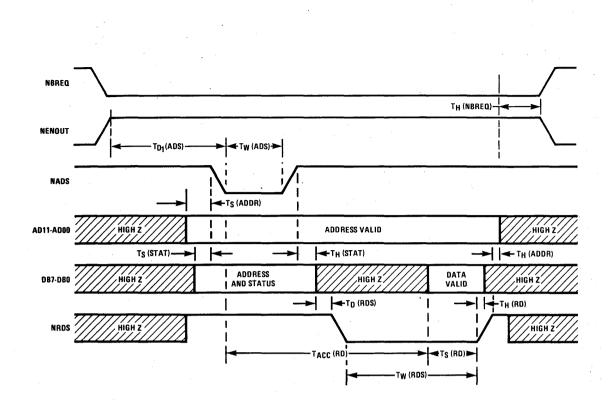

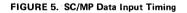

| Address and Input/Output Status<br>(see figures 5 and 6)<br>TD1 (ADS) |                                                                     |                                  | 3T <sub>C</sub> /2 | ns       |

|                                                                       |                                                                     | (T <sub>C</sub> /2) - 50         |                    | ns       |

| T <sub>S</sub> (ADDR)                                                 | · · · · · · · · · · · · · · · · · · ·                               | (T <sub>C</sub> /2) -165         |                    | ns       |

| T <sub>H</sub> (ADDR)                                                 |                                                                     | 50                               |                    | ns       |

| T <sub>S</sub> (STAT)                                                 | · · ·                                                               | (T <sub>C</sub> /2) -150         |                    | ns       |

| T <sub>H</sub> (STAT)                                                 | · · · · · · · · · · · · · · · · · · ·                               | 50                               |                    | ns       |

| T <sub>H</sub> (NBREQ)                                                |                                                                     | 0                                |                    | ns       |

| Data Input Cycle (see figure 5)                                       |                                                                     |                                  |                    |          |

| T <sub>D</sub> (RDS)                                                  |                                                                     | 0                                |                    | ns       |

| T <sub>W</sub> (RDS)                                                  |                                                                     | T <sub>C</sub> + 50              |                    | ns       |

| T <sub>S</sub> (RD)<br>T <sub>H</sub> (RD)                            |                                                                     | 175<br>0                         |                    | ns       |

| T <sub>ACC</sub> (RD)                                                 | ······································                              | 2T <sub>C</sub> - 200            |                    | ns<br>ns |

| Data Output Cycle (see figure 6)                                      |                                                                     |                                  |                    |          |

| T <sub>D</sub> (WDS)<br>T <sub>W</sub> (WDS)                          |                                                                     | T <sub>C</sub> - 50              |                    | ns       |

|                                                                       |                                                                     | T <sub>C</sub>                   |                    | ns       |

| T <sub>S</sub> (WD)<br>T <sub>H</sub> (WD)                            |                                                                     | (T <sub>C</sub> /2) – 200<br>100 |                    |          |

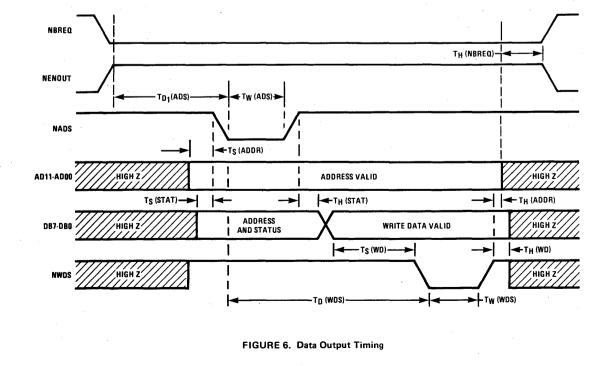

| Input/Output Cycle Extend<br>(see figure 7)                           |                                                                     |                                  |                    | ns       |

| T <sub>S</sub> (HOLD)                                                 |                                                                     | 200                              | 075                | ns       |

| T <sub>D1</sub> (HOLD)                                                |                                                                     | 130                              | 275                | ns       |

| T <sub>D2</sub> (HOLD)<br>T <sub>W</sub> (HOLD)                       |                                                                     |                                  | 350                | ns       |

| T <sub>H</sub> (HOLD)                                                 |                                                                     | 0                                | ∞                  | ns       |

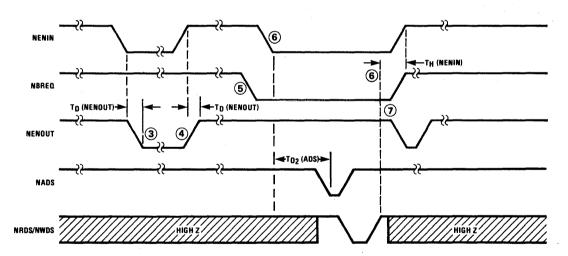

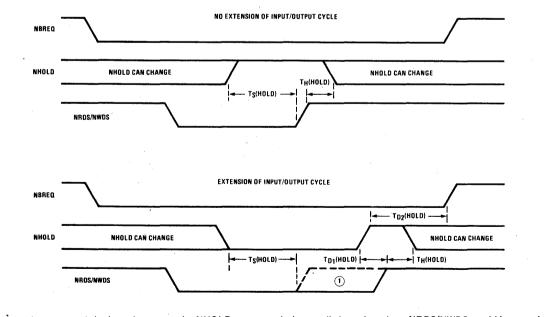

| Bus Access (see figure 4)                                             | · · · · · · · · · · · · · · · · · · ·                               |                                  |                    | ns       |

| T <sub>D</sub> (NENOUT)                                               |                                                                     |                                  | 150                | ns       |

| T <sub>D2</sub> (ADS)                                                 |                                                                     | T <sub>C</sub> /2                | 3T <sub>C</sub> /2 | ns       |

| T <sub>H</sub> (NENIN)                                                |                                                                     | 0                                |                    | ns       |

| Output Load Capacitance<br>XOUT                                       |                                                                     |                                  | 30                 | pF       |

| All Other Output Pins                                                 |                                                                     |                                  | 75                 | pF       |

limited to those conditions specified under electrical characteristics.

Note 2: NBREQ is an input/output signal that requires an external resistor to V<sub>CC</sub>. Note 3: All times measured from valid Logic "0" level = 0.8 V or valid Logic "1" level = 2.0 V. Note 4: T<sub>C</sub> is the time period for two clock cycles of the on-chip or external oscillator (T<sub>C</sub> =  $2/f_X$ ). Refer to paragraph titled Timing Control for detailed definition.

Note 5: All times measured with a 50% duty cycle on the external clock.

## functional description

SC/MP is a self-contained general-purpose microprocessor designed for ease of implementation in stand-alone, DMA (Direct Memory Access), and multiprocessor applications. Communications between SC/MP and external memory/ peripheral devices are effected via a 12-bit dedicated address bus and an 8-bit bidirectional data bus. During the address interval of each input/output cycle, SC/MP employs both busses to provide a 16-bit address output: the 12 least significant address bits are sent out over the 12-bit address bus and the 4 most significant address bits are sent out over the 8-bit data bus along with 4 status bits. Separate strobe outputs from SC/MP (NADS, NWDS, NRDS) indicate when valid address information is present on the two busses, and when valid input/ output memory or peripheral data are present on the 8-bit bus. To further extend flexibility of application, serial data input/output ports are also provided so that serial data transfers can be effected under program control. The remaining input/output signals shown in figure 1 are dedicated to general-purpose control and status functions, including initialization, bus management, microprocessor halt, interrupt request, input/ output cycle extension, and user-specified hardware/ software interface functions. A detailed description of each input/output signal is provided in table 1.

### TABLE 1. Input/Output Signal Description

| Signal<br>Mnemonic | Functional Name                          | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|--------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NRST               | Reset Input                              | Set high for normal operation. When set low, aborts in-process operations. When returned high, internal control circuit zeroes all programmer-accessible registers; then, first instruction is fetched from memory location 000116.                                                                                                                                                  |  |  |  |

| CONT               | Continue Input                           | When set high, enables normal execution of program stored in<br>external memory. When set low, SC/MP operation is suspended<br>(after completion of current instruction) without loss of internal<br>status.                                                                                                                                                                         |  |  |  |

| NBREQ              | Bus Request Input/Output                 | Associated with SC/MP internal allocation logic for system bus. Can be used as bus request output or bus busy input. Requires external load resistor to $V_{CC}$ .                                                                                                                                                                                                                   |  |  |  |

| NENIN              | Enable Input                             | Associated with SC/MP internal allocation logic for system bus.<br>When set low, SC/MP is granted access to system busses. When<br>set high, places system busses in high-impedance (TRI-STATE®)<br>mode.                                                                                                                                                                            |  |  |  |

| NENOUT             | Enable Output                            | Associated with SC/MP internal allocation logic for system bus.<br>Set low when NENIN is low and SC/MP is not using system<br>busses (NBREQ-high). Set high at all other times.                                                                                                                                                                                                      |  |  |  |

| NADS               | Address Strobe Output                    | Active-low strobe. While low, indicates that valid address and status output are present on system busses.                                                                                                                                                                                                                                                                           |  |  |  |

| NRDS               | Read Strobe Output                       | Active-low strobe. On trailing edge, data are input to SC/MP from<br>8-bit bidirectional data bus. High-impedance (TRI-STATE®)<br>output when input/output cycle is not in progress.                                                                                                                                                                                                 |  |  |  |

| NWDS               | Write Strobe Output                      | Active-low strobe. While low, indicates that valid output data are present on 8-bit bidirectional data bus. High-impedance (TRI-STATE <sup>®</sup> ) output when input/output cycle not in progress.                                                                                                                                                                                 |  |  |  |

| NHOLD              | Input/Output Cycle Extend<br>Input       | When set low prior to trailing edge of NRDS or NWDS strobe,<br>stretches strobe to extend input/output cycle; that is, strobe is<br>held low until NHOLD signal is returned high.                                                                                                                                                                                                    |  |  |  |

| SENSE A            | Sense/Interrupt Request<br>Input         | Serves as interrupt request input when SC/MP internal IE<br>(Interrupt Enable) flag is set. When IE flag is reset, serves as user-<br>designated sense condition input. Sense condition testing is<br>effected by copying status register to accumulator.                                                                                                                            |  |  |  |

| SENSE B            | Sense Input                              | User-designated sense-condition input. Sense-condition testing is effected by copying status register to accumulator.                                                                                                                                                                                                                                                                |  |  |  |

| SIN .              | Serial Input to E Register               | Under software control, data on this line are right-shifted into E register by execution of SIO instruction.                                                                                                                                                                                                                                                                         |  |  |  |

| SOUT               | Serial Output from E<br>Register         | Under software control, data are right-shifted onto this line from E register by execution of SIO instruction. Each data bit remains latched until execution of next SIO instruction.                                                                                                                                                                                                |  |  |  |

| FLAGS<br>0, 1, 2   | Flag Outputs                             | User-designated general-purpose flag outputs of status register.<br>Under program control, flags can be set and reset by copying<br>accumulator to status register.                                                                                                                                                                                                                  |  |  |  |

| AD00-<br>AD11      | Address Bit 00 through<br>Address Bit 11 | Twelve TRI-STATE <sup>®</sup> address output lines. SC/MP outputs 12<br>least significant address bits on this bus when NADS strobe is low.<br>Address bits are then held valid until trailing edge of read (NRDS)<br>or write (NWDS) strobes. After trailing edge of NRDS or NWDS<br>strobe, bus is set to high-impedance (TRI-STATE <sup>®</sup> ) mode until<br>next NADS strobe. |  |  |  |

## NOTE:

The 8-bit bidirectional data bus is set to the high-impedance (TRI-STATE<sup>®</sup>) mode except when it is actually in use by SC/MP (NADS, NRDS, or NWDS low). During the addressing interval of each input/output cycle (NADS low), SC/MP provides address and status outputs over the bus; during the ensuing data-transfer interval (NRDS or NWDS low), 8-bit input or output data bytes are routed over the bus.

1

| Signal Mnemonic/ |                 | Output at NADS Time                                                                                                                                                                                                  | Input at                                         | Output at                           |  |

|------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|--|

| Pin Designation  | Functional Name | Description                                                                                                                                                                                                          | NRDS Time                                        | NWDS Time                           |  |

| , DB0            | Address Bit 12  | Fourth most significant bit of 16-bit address.                                                                                                                                                                       |                                                  | 1                                   |  |

| DB1              | Address Bit 13  | Third most significant bit of 16-bit address.                                                                                                                                                                        |                                                  |                                     |  |

| DB2              | Address Bit 14  | Second most significant bit of 16-bit address.                                                                                                                                                                       | Input data                                       | Output data                         |  |

| DB3              | Address Bit 15  | Most significant bit of 16-bit address.                                                                                                                                                                              | are expected                                     | are valid                           |  |

| DB4              | R-Flag          | When high, data input cycle is start-<br>ing; when low, data output cycle is<br>starting.                                                                                                                            | on the eight<br>(DB0-DB7)<br><sup>lines.</sup> l | on the eight<br>(DB0-DB7)<br>lines. |  |

| DB5              | I-Flag          | When high, first byte of instruction is being fetched.                                                                                                                                                               |                                                  |                                     |  |

| DB6              | D-Flag          | When high, indicates delay cycle is<br>starting; that is, second byte of DLY<br>instruction is being fetched.                                                                                                        |                                                  |                                     |  |

| DB7              | H-Flag          | When high, indicates that Halt<br>Instruction has been executed. (In<br>some system configurations, the H-<br>Flag output is latched and, in<br>conjunction with the CONTinue<br>input, provides a programmed halt.) | (AD12-HFLG                                       | ce (open circuit)<br>C/MP does not  |  |

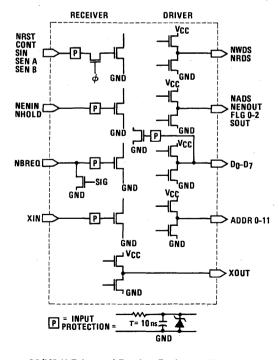

## DRIVERS AND RECEIVERS

Equivalent circuits for SC/MP drivers and receivers are shown below. All inputs have static charge protection circuits consisting of an RC filter and voltage clamp. These devices still should be handled with care, as the protection circuits can be destroyed by excessive static charge.

SC/MP-II Driver and Receiver Equivalent Circuits

### TIMING CONTROL

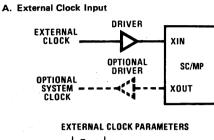

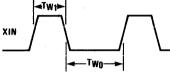

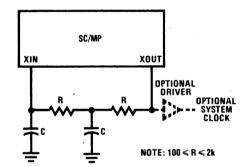

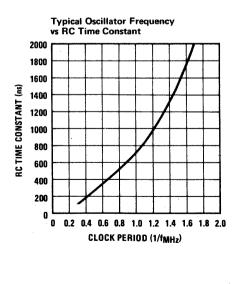

All necessary timing signals are provided by a three-stage inverter ring oscillator contained on the SC/MP chip. Two control pins, XIN and XOUT, permit the frequency of the oscillator to be controlled by any of the following methods:

- By leaving the XOUT pin unterminated and driving the XIN pin with an externally generated TTL clock that conforms to the parameters shown in figure 2A. For this method, the frequency of the oscillator is equal to the frequency of the external clock input.

- 2. By connecting a resistor-capacitor feedback network between the XIN and XOUT pins and GND as shown in figure 2B.

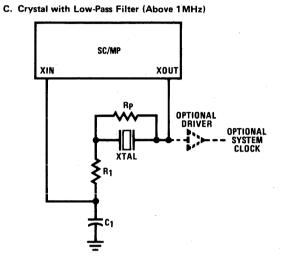

- 3. By connecting a crystal with low-pass filter network between the XIN and XOUT pins and GND as shown in figure 2C (for above 1 megahertz) or figure 2D (for 1 megahertz or below). For this method, the frequency of the oscillator is equal to the resonant frequency of the crystal and the low-pass filter prevents unwanted harmonic oscillations.

In addition to illustrating appropriate frequency-control networks for the on-chip oscillator, figures 2A through 2D also show how an optional driver may be used to derive a system clock from the oscillator signal present at the XOUT pin. For reference purposes, the timing relationship between the XOUT signal and the NADS strobe is shown in figure 3.

In the discussions that follow, instruction execution and input/output timing are described in terms of microcycles.

The time interval of a microcycle is four times the period of the oscillator; that is:

period of one microcycle =  $2T_C$

$$T_{C} = 2(\frac{1}{f_{osc}}) = 2(\frac{1}{f_{res}}) = 2(\frac{1}{f_{XIN}})$$

where:

T<sub>C</sub> = time period for two cycles of on-chip or external oscillator

fosc = frequency of on-chip oscillator

fres = resonant frequency of crystal connected between XIN and XOUT pins

fXIN s frequency of external clock applied to XIN pin

**B. Resistor-Capacitor Feedback Network**

FIGURE 2. Frequency Control Networks for On-Chip Oscillator

Suggested values for Crystal with Low-Pass Filter Network.

| Crystal | RP            | C <sub>1</sub> | R <sub>1</sub> |

|---------|---------------|----------------|----------------|

| 2MHz    | 100k $\Omega$ | 56pF           | 1kΩ            |

| 3.58MHz | 100kΩ         | 27pF           | 1kΩ            |

| 4MHz    | 100k $\Omega$ | 27pF           | 1kΩ            |

XTAL is parallel resonant with maximum series resonance equal to  $1\,k\Omega.$

#### D. Crystal with Low-Pass Filter (1MHz or Below)

### INSTRUCTION FORMAT

The SC/MP instruction repertoire includes both singlebyte and double-byte instructions. A single-byte instruction consists of an 8-bit operation code that specifies an operation that SC/MP can execute without further reference to memory. A double-byte instruction consists of an 8-bit operation code and an 8-bit data or displacement field. When the second byte represents a data field, the data are processed by SC/MP during execution of the instruction, thereby eliminating the need for further memory references. When the second byte represents a displacement value, it is used to calculate a memory address that will be accessed (written into or read from) during execution of the instruction (refer to Addressing).

#### DATA STORAGE

As shown in figure 1, SC/MP provides ten internal registers, seven of which are accessible to the programmer. The purpose and function of these registers are described below.

**Program Counter** – The program counter is a 16-bit register that contains the address of the instruction being executed. The contents of this register are automatically incremented by one just before each instruction is fetched from memory to enable sequential execution of the stored instructions. Under program control, the contents of this register also may be modified or exchanged with the contents of a pointer register to effect subroutine calls and program branches.

#### NOTE:

The 16-bit address output of the program counter consists of a 4-bit high-order address and a 12-bit low-order address. When the program counter is incremented at the start of each instruction fetch input/output cycle, only the 12 low-order bits are affected; no carry is provided to the 4 high-order bits. For systems employing memories of 4k or less, the high-order bits can be ignored as they are set to 000016 following initialization. For systems employing larger memories, the contents of a pointer register can be modified to select the desired 4k block of memory.

**Pointer Registers** – The pointer registers are 16-bit general-purpose registers that normally are loaded under program control with reference addresses that serve as page pointers, stack pointers, and subroutine pointers. In applications having minimal memory addressing requirements, these registers may be used alternately as data storage registers.

#### NOTE:

When interrupt requests are enabled, pointer register 3 is automatically referenced by the internal microprogram for formation of the starting address of the user-generated interrupt service routine. (See figure 9.) In this case, the contents of pointer register 3 must be set to one less than the memory location of the first instruction in the interrupt service routine.

Accumulator — The 8-bit accumulator (AC) is the primary working register of SC/MP. It is used for performing and storing the results of arithmetic and logic operations as well as for data transfers, shifts, rotates, and data exchanges with the program counter, the pointer registers, and the status register. **Extension Register** – The extension register is used both for serial input/output data transfers and with the accumulator to effect arithmetic, logic, and data-transfer operations. If the second byte of an indexed or auto-indexed memory-reference instruction (refer to Addressing) equals  $-128_{10}$ , the contents of the extension register are used as the displacement value for address formation.

Status Register – The status register provides storage for arithmetic, control, and software status flags. For moredetailed information on the function of this register, refer to Status Register under the description of the Arithmetic and Logic Unit.

**Instruction Register** — The 8-bit instruction register is not accessible to the programmer. During the fetch phase of each instruction cycle, this register is loaded with the 8-bit instruction operation code retrieved from memory (for a single-byte instruction or the first byte of a double-byte instruction).

Data Input/Output Register – The data input/output register is not accessible to the programmer. It is used for temporary storage of all input/output data received via or transmitted over the 8-bit bidirectional data bus during the data-transfer interval of each input/output cycle (NRDS or NWDS low).

Address Register – The 16-bit address register is not accessible to the programmer. It is used for temporary storage of the 16-bit address transmitted during an input/ output cycle.

### ARITHMETIC AND LOGIC UNIT

The Arithmetic and Logic Unit (ALU) provides the datamanipulation capability that is an essential feature of any microprocessor. The operations provided by the ALU include OR, XOR, increment, decrement, binary addition, and decimal addition. For decimal addition, the data inputs to the ALU are treated as two 4-bit BCD digits, thereby eliminating the program-storage and execution time required to perform BCD to binary conversion.

#### BUS TRANSFER LOGIC

The bus transfer logic processes the gating and function control outputs of the instruction-decode logic to provide the shift-right (with link, without link, or with serial input data), rotate (with or without link), and bus-exchange functions necessary for data movement between the SC/MP internal read and write busses. A general summary of the data-manipulation capabilities available to the programmer follows.

1. Either the low-order or the high-order byte of any pointer register can be exchanged with the contents of the 8-bit accumulator. Thus, data exchanges between the pointer registers can be effected one byte at a time via the accumulator.

2. The contents of the program counter can be directly exchanged with the contents of any pointer register.

3. The contents of the extension register can be loaded into the accumulator or can be exchanged with the contents of the accumulator. When the accumulator is loaded from the extension register, the original contents of the accumulator are lost. 4. The contents of the status register can be copied into the accumulator to enable status modification or conditional-branch testing. When the status register is copied into the accumulator, the contents of the status register are not altered but the original contents of the accumulator are lost.

5. The contents of the accumulator can be copied into the status register to change the outputs of the status register, except for status bits 4 and 5 (Sense A and B inputs to SC/MP). Since these are read-only bits, they are not affected by data movements internal to SC/MP. Copying the accumulator into the status register does not alter the contents of the accumulator.

### NOTE:

The flag 0, 1, and 2 outputs of the status register serve as latched flags; in other words, they are set to the specified state when the contents of the accumulator are copied into the status register, and they remain in the specified state until the contents of the status register are modified again under program control.

### STATUS REGISTER

The function of each bit in the status register is described briefly below.

| 7    | 6  | 5  | 4  | 3  | 2  | 1   | 0  |  |

|------|----|----|----|----|----|-----|----|--|

| CY/L | ov | SB | SA | IE | F2 | .F1 | FO |  |

User Flag 0 – User-assigned general-purpose status bit for implementation as software status bit or in system control applications. This status bit is available as an external output from SC/MP.

User Flag 1 - Same as User Flag 0.

User Flag 2 - Same as User Flag 0.

**Interrupt Enable Flag** – Internal status bit that is set and reset under program control. When set, SC/MP recognizes external interrupt requests received via Sense A input. When reset, inhibits SC/MP from recognizing interrupt requests.

**Sense A** – General-purpose status input for sensing external conditions. When IE flag is reset, this bit can be tested by copying status register to accumulator. When IE flag is set, this bit serves as interrupt request input causing SC/MP to automatically branch to user-generated interrupt-service routine in response to high input.

Sense B – Same as Sense A except that it is not tested for interrupt status.

#### NOTE:

Sense A and B inputs are read-only bits. Thus, they are not affected when the contents of the accumulator are copied into the status register.

**Overflow (OV)** – This bit is set if an arithmetic overflow occurs during an add (ADD, ADI, or ADE) or a complement-and-add instruction (CAD, CAI, or CAE). It is not affected by the decimal-add instructions (DAD, DAI, or DAE).

**Carry/Link (CY/L)** — This bit is set if a carry from the most significant bit occurs during an add, complementand-add, or decimal-add instruction. Thus, it serves as a carry input to the next add instruction. In addition, it is included in the Shift Right with Link (SRL) and Rotate Right with Link (RRL) instructions.

## CONTROL

The operation of the SC/MP microprocessor consists of repeatedly accessing or fetching instructions from the program stored in external memory and executing the operations specified by the instructions. These two steps are carried out under the control of an internal microprogram. (SC/MP is not user-microprogrammable.) The microprogram is similar to a state table specifying the series of states of system control signals necessary to carry out each instruction. Microprogram storage is provided in the instruction decode and control logic. and microprogram routines are implemented to fetch and execute instructions. The fetch routine first increments the program counter, and then causes the instruction address to be transferred from the program counter to the system busses via the output address register. The microprogram next initiates an input data transfer. When the instruction operation code is subsequently placed on the 8-bit data bus (single-byte instruction or first byte of double-byte instruction), the operation code is loaded into the instruction register. The operation code is then partially decoded to determine whether the instruction contains a second byte. If it does, a second input data transfer is effected to load the next byte in the data input/output register.

After the complete instruction is stored in the instruction and/or data input/output register(s), the instruction decoder transforms the instruction operation code into the address of the appropriate instruction-execution routine contained in the internal microprogram. The microprogram then branches to the specified internal address to initiate execution of the instruction. The resulting execution routine comprises one or more microinstructions that implement the required functions. For example, the first microcycle of an Extension Register Add Instruction (ADE) causes the contents of the extension register to be gated onto the read bus, transferred to the write bus via the bus control logic, and then written into the data input/output register. The next microcycle causes the contents of the accumulator to be gated onto the read bus, the contents of the read bus to be added to the contents of the data input/ output register via the ALU, and the resultant output of the ALU to be written into the accumulator via the write bus. The final step of the execution routine is a jump back to the fetch routine to access the next instruction.

#### INITIALIZATION

Since SC/MP may power up in a random condition, the following power-up and initialization procedure is recommended.

1. Apply power (GND and V<sub>CC</sub>) and set NRST low.

#### NOTE:

Allow ample time (typically, 250 ms) for the oscillator and the internal clocks to stabilize. In systems where NRST is set low after turning on power, NRST must remain low for a minimum of  $4T_{\rm C}$ . While NRST is low, any in-process operations are aborted automatically. When NRST is low, strobes and address and data busses are in the Non-I/O state (high-Z state).

ROCESSOR

2. Set NRST high. If the rise time of this input is too slow, the processor, first, will initialize and execute a few instructions and, then, will reinitialize. If the application is such that multiple initialization is undesireable, NRST should be brought high at a minimum rate of 2 volts per microcycle.

#### NOTE:

This causes the SC/MP internal control circuit to set the contents of all programmer-accessible registers to zero. Thus, when SC/MP is granted access to the system busses following initialization, the first instruction is fetched *always* from memory location 0001<sub>16</sub>. The NBREQ output goes low, indicating the start of this input/output cycle; this occurs at a time within 13T<sub>C</sub> after NRST is set high. Normal execution of the program continues as long as NRST remains high.

## parallel data transfers

Parallel data transfers occur during each instruction fetch and during the ensuing read/write cycle associated with execution of the memory-reference instructions. This class of instruction could perhaps more properly be called the "Input/Output Reference Class" in the case of the SC/MP microprocessor, since all data transfers, whether with memory, peripheral devices, or a central processor data bus, occur through the execution of these instructions. This unified bus structure is in contrast with many other microprocessors and minicomputers that have one instruction type (input/output class) for communication with peripheral devices and another instruction type (memory reference class) for communication with memories. The advantage of the approach taken by SC/MP is that a wider variety of instructions (the entire memory-reference class) is available for communications with peripherals. Thus, the LD and ST (Load and Store) instructions can be used for basic transfers, the ILD and DLD (increment/decrement and load) instructions can be used for indexing peripheral registers, and the remaining memory reference instructions can be used, as required, for "one-step" retrieval and processing of peripheral input data.

### **BUS UTILIZATION**

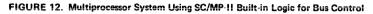

The bus utilization of SC/MP is shown in table 2.

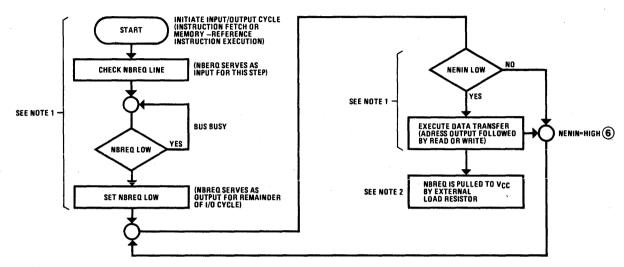

NBREQ, NENIN, and NENOUT are active and bus access is controlled as shown in figure 4. If NENIN is returned high during an input/output cycle, the input/ output cycle is repeated when NENIN is again returned low.

During an ILD or DLD instruction, SC/MP does not relinquish the bus between the loading of the data and the storing of the modified data. If NENIN is brought high after the data have been loaded, the load portion of the cycle is not repeated when NENIN is returned low.

#### **BUS ACCESS**

Before SC/MP can initiate parallel data transfers with memory or peripheral devices, it must have access to the system address and data busses. Three of the SC/MP input/output signals are associated with bus control: NBREQ, NENIN, and NENOUT. For simple stand-alone applications, the NENOUT signal can be ignored and the NENIN signal can be tied to GND to allow the SC/MP microprocessor to have continual access to the system busses. The NBREQ input/output line then goes low during each input/output cycle as shown in figures 5 and 6 to indicate when SC/MP is actually using the system busses.

#### NOTE:

The NBREQ input/output line must be tied to V<sub>CC</sub> via an external load resistor to allow normal operation of the SC/MP microprocessor.

For DMA and multiprocessor applications, the NBREQ, NENIN, and NENOUT signals can be interconnected in various configurations to allow bus access to be granted to requesting devices according to user-specified priorities. Figure 4 illustrates the general sequence in which these signals are processed by SC/MP to gain access to the system busses and to indicate when the busses are actually being used.

### **INPUT/OUTPUT CYCLE**

Once SC/MP has control of the system busses, the actual input/output cycle begins. As shown in figures 5 and 6, the functions of memory addressing, data reading, and data writing are implemented, respectively, by the address strobe (NADS), the read strobe (NRDS), and the write strobe (NWDS). Note that the NBREQ signal is reset high at the end of the input/output cycle to indicate that the system busses are now free for use by the highest-priority requesting device.

The first operation that SC/MP performs for each input/ output cycle is to load the 12 least significant address bits onto the 12-bit address bus, and the 4 most significant address bits along with 4 status bits onto the 8-bit data bus. At the same time, SC/MP sets the NADS output low to indicate that the address and the status information are valid. The low-order address on the 12-bit bus is then held valid for the duration of the input/output cycle; the high-order address and the status information on the 8-bit bus remain valid only while NADS is low. While valid, the status bits have the following significance:

**RFLG** — When high, indicates that input/output cycle is read cycle; when low, indicates that input/output cycle is write cycle.

**IFLG** – Set high to indicate that instruction operation code (single-byte instruction or first byte of double-byte instruction) will be output from memory following NADS.

**DFLG** – Set high only when second byte of Delay Instruction is to be read from memory following NADS. Execution of the Delay Instruction then starts at trailing edge of NRDS. Upon completion, SC/MP provides NADS output to initiate next input/output cycle if bus access is granted. Time in microcycles from leading edge of delay flag to leading edge of subsequent NADS output is computed from the following formula:

$Delay = [9 + 2(AC) + 2 disp + 2^9 disp] microcycles$

where

- (AC) = unsigned contents of accumulator

- disp = unsigned displacement value contained in second byte of Delay Instruction

The time derived from the above formula does not include the four microcycles required to fetch the first byte of the Delay Instruction. Thus, when the Delay Instruction is used for software timing, total instruction execution time equals  $[13 + 2(AC) + 2 \text{ disp} + 2^9 \text{ disp}]$  microcycles.

#### NOTE:

When Halt Instruction is executed, instruction decode and control logic inhibits incrementing of program counter for one input/output cycle. Thus, Halt Instruction is read from memory a second time to enable generation of HFLG output, but no

further processing of Halt Instruction occurs. In effect, this procedure ensures HFLG is output in advance of the next instruction to be fetched from memory.

HFLG – Set high only during addressing interval of read cycle that follows Halt Instruction. HFLG may be used to cause user-provided external logic to set the CONT input low, and thereby to effect a programmed halt. Since HFLG read cycle precedes the next instruction

A. NBREQ and NENIN Processing Sequence

B. NBREQ, NENIN, and NENOUT Timing

Note 1: NENOUT is always high while SC/MP is actually using bus; that is, NENIN input and NBREQ output are low.

- Note 2: When SC/MP is not using bus (NBREQ output or NENIN input high), NENOUT is held in same state as NENIN input.

- Note 3: NENOUT goes low to indicate that SC/MP was granted access to bus (NENIN low) but is not using bus.

- Note 4: NENOUT goes high in response to high NENIN input.

- Note 5: SC/MP generates bus request; bus access not granted because NENIN high.

Note 6: NENIN goes low. Bus access now granted and input/output cycle actually initiated. If NENIN is set high while SC/MP has access to the bus, the address and data ports will go to the high-impedance (Tri-State®) state, but NBREQ will remain low. When NENIN is subsequently set low, the input/output cycle will begin again.

Note 7: Input/output cycle completed. NENOUT goes low to indicate that SC/MP granted access to bus but not using bus. If NENIN had been set high before completion of input/output cycle, NENOUT would have remained high.

FIGURE 4. Bus Access Control

Note: Timing is valid when NENIN is low before NBREQ is set low by SC/MP; see figure 4 for NADS timing when NENIN is set low after NBREQ.

National Semiconductor

MICROPROCESSOR

fetch, termination of programmed halt enables fetch of first instruction that follows Halt Instruction.

After resetting the NADS output, SC/MP generates an NRDS or NWDS strobe, respectively, to initiate a datainput (read) or data-output (write) operation. For a read operation, input data are strobed into SC/MP from the 8-bit bus on the trailing edge of the NRDS strobe. For a write operation, SC/MP places valid output data on the 8-bit bus on the leading edge of the NWDS strobe. After resetting the NRDS or NWDS strobe to complete the data transfer, SC/MP then resets the NBREQ signal to indicate that the system busses are free for use by another controller.

### **INPUT/OUTPUT CYCLE EXTENSION**

As shown in figure 7, the NHOLD signal may be set low prior to the trailing edge of the NRDS or NWDS strobe to cause SC/MP to lengthen the input/output cycle by holding the strobe active until after the NHOLD signal is returned high. Since there is no restriction on the maximum duration of the NHOLD signal, it can be used in a variety of applications ranging from accommodation of memories/peripherals with long access times to singlecycle control of the operating program for software debug purposes.

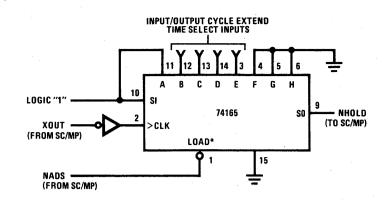

Figure 8 illustrates a typical circuit that may be used to generate an NHOLD signal of repeatable duration. The circuit shown employs a DM74165 8-Bit Parallel In/ Serial Out Shift Register to allow selection of an input/ output cycle extend time that ranges from  $T_C/2$  to  $2T_C$  in increments of  $T_C/2$ . Functional operation of the circuit is controlled by the NADS strobe and XOUT signals. Each time that the NADS strobe goes low, the data present at the A through H terminals are loaded into the shift register in parallel. When the NADS strobe subsequently returns high, the data are then shifted out serially on the positive-to-negative transitions of XOUT. Thus, the NHOLD output of the circuit is set low on the leading edge of each NADS strobe and, as shown in the chart that accompanies the circuit diagram, it remains low for a time period ranging from three clock cycles minimum (B, C, D, and E inputs = Logic "1") to seven clock cycles maximum (B, C, D, and E inputs = Logic "0").

It is important to note that instruction execution time is increased whenever an input/output cycle is extended via the NHOLD signal. For purposes of computing the increase in instruction execution time, it is necessary to distinguish between the terms *Input/Output Cycle Delay Period* and *Input/Output Cycle Extend Time*. The term *Input/Output Cycle Delay Period* refers to the time that the NRDS/NWDS strobe is actually "stretched" to provide the required memory or peripheral access time. The term *Input/Output Cycle Extend Time* refers to the additional number of microcycles required by the internal SC/MP microprogram to complete the extended input/output cycle; that is:

| Input/Output Cycle<br>Delay Period                                   | Input/Output Cycle<br>Extend Time |

|----------------------------------------------------------------------|-----------------------------------|

| T <sub>C</sub> /2 through 2T <sub>C</sub> (> 0 $\leq$ 1 $\mu$ cycle) | 1 μcycle                          |

| $5T_{C}/2$ through $4T_{C}$ (> 1 $\leq$ 2 $\mu$ cycle                | es) 2 µcycles                     |

| $9T_{C}/2$ through $6T_{C}$ (> 2 $\leq$ 3 $\mu$ cycle                | es) 3 µcycles                     |

| etc.                                                                 | etc.                              |

The total increase in instruction execution time, therefore, is equal to the *Input/Output Cycle Extend Time* multiplied by the total number of input/output cycles associated with the instruction. For example, a DLD Instruction is normally executed in 22 microcycles. Since this instruction employs three read input/output cycles and one write input/output cycle, an *Input/Output Cycle Extend Time* of one microcycle would increase total DLD Instruction execution time to 26 microcycles.

Note 1: In order to extend the input/output cycle, NHOLD must remain low until the point where NRDS/NWDS would have made a low-to-high transition with NHOLD inactive. Dashed line indicates the trailing edge of NRDS/NWDS when NHOLD is not active.

FIGURE 7. NHOLD Timing

National Semiconductor

| Data Inputs NHOLD Duration |                   | Input/Ou           | tput Cycle                    | Required Memory                        |

|----------------------------|-------------------|--------------------|-------------------------------|----------------------------------------|

| BCDE                       | (in clock cycles) | Delay Period       | Extend Time<br>in Microcycles | Access Time<br>[T <sub>ACC</sub> (RD)] |

| 1 1 1 1                    | 3                 | 0                  | 0                             | 2T <sub>C</sub> – 200                  |

| 1 1 1 0                    | 4                 | T <sub>C</sub> /2  | 1                             | (5T <sub>C</sub> /2) – 200             |

| 1 1 0 0                    | 5                 | TC                 | 1                             | 3T <sub>C</sub> – 200                  |

| 1000                       | 6                 | 3T <sub>C</sub> /2 | . 1                           | (7T <sub>C</sub> /2) – 200             |

| 0000                       | 7                 | 2TC                | 1                             | 4T <sub>C</sub> – 200                  |

#### FIGURE 8. Typical NHOLD Control Circuit

## serial data transfers

Serial input/output data transfers can be used efficiently with very slow input/output peripherals such as X-Y plotters, teletypewriters, slow-speed printers, and so forth. Such transfers can be effected in any of the following manners:

1. By assigning serial input/output functions to the extension register via the SIO (Serial Input/Output) Instruction. When this instruction is executed, the contents of the extension register are shifted right one bit. At the same time, data present on the SIN line are shifted into bit position 7 of the extension register and the original contents of bit position 0 are shifted into a flip-flop to provide a latched output of the SOUT line. The SOUT data are then held latched until the next SIO instruction is executed.

2. By using one of the status flags as an output data bit and one of the sense lines as an input data bit.

3. By implementing external logic such that only one line of the 8-bit data input/output bus is used.

For synchronous systems, serial data input/output timing may be provided by program loops that employ the delay instruction, or by using one or more of the transfer instructions (see table 2) to test the output of an external timing circuit. For asynchronous systems, one of the sense inputs can be used for testing bit-received/ready status and a pulsed flag output can be provided, under program control, for peripheral indexing each time that a data bit is actually shifted in or out.

Systems that have several input/output devices must be multiplexed; device selection can then be accomplished using the status flag outputs of SC/MP, or by using

parallel input/output commands to load an external latch. Systems that do not require serial input/output capability can employ the SIN and SOUT lines as a sense input and flag output, respectively.

### interrupts

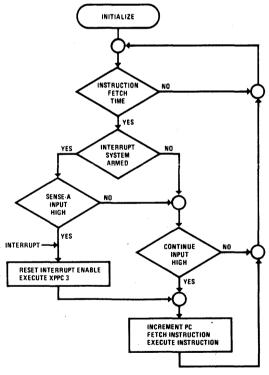

When the internal interrupt enable (IE) flag is set under program control, the Sense A line is enabled to serve as an interrupt request input; when the IE flag is reset, SC/MP is inhibited from detecting interrupts. Thus, while the IE flag is set, the Sense A input is tested prior to the fetch phase of each instruction as shown in figure 9. Upon detection of an interrupt request (Sense A high), the following events occur automatically.

1. The status register IE flag is reset to prevent SC/MP from responding to any further interrupt requests. Interrupt request capability can then be reenabled during or at the end of the ensuing user-generated interrupt service routine via the IEN (Enable Interrupt) Instruction or by copying the accumulator into the status register.

2. The contents of the program counter are exchanged with the contents of the pointer register 3.

3. The contents of the program counter are incremented by one to address the first instruction of the usergenerated interrupt service routine.

The interrupt system must be armed before interrupts are enabled. This is accomplished as follows:

1. First, the Interrupt Enable Bit in the Status Register is set true by executing either an Enable Interrupt Instruction (IEN) or a Copy Accumulator to Status Register Instruction (CAS). 2. Second, one additional instruction is fetched and executed.

A return from interrupt is accomplished by executing two instructions: Enable Interrupt (IEN) immediately followed by Exchange Pointer 3 with Program Counter (XPPC 3).

## microprocessor halt

The CONT input to SC/MP is provided to enable suspension of operation without loss of internal status. Processing of the CONT input is shown in figure 9. Since this is an asynchronous input, it can be controlled by external timing logic, or as stated previously, the HALT flag output that appears on the 8-bit data bus (during the read cycle that follows execution of a Halt Instruction) can be used with an external circuit to effect a programmed halt condition. Note that when an interrupt request is detected while the CONT input is low, the first instruction of the user-generated interrupt service routine is automatically executed. Thus, the first instruction of the interrupt service routine can be used to reset the external CONT input logic and, thereby, to terminate the microprocessor halt condition if so desired.

After execution of an instruction, the CONT input must be high for a minimum time of  $2T_C$  (1 microcycle) in order to fetch and execute the next instruction.

FIGURE 9.

Microprocessor Halt and Interrupt Request Input Processing

### instruction set

The SC/MP instruction set provides the general-purpose user of microprocessors a powerful programming capability along with above-average flexibility and speed. The instruction set consists of 46 instructions, which comprise eight general categories. A listing of the complete instruction set is provided in table 2; typical instruction execution times are given in table 3, and notations and symbols used as shorthand expressions of instruction capability are defined in table 4.

#### ADDRESSING

During execution, instructions and data defined in a program are stored into and loaded from specific memory locations, the accumulator, or selected registers. Because SC/MP, memory (read/write and read-only), and peripherals are on a common data bus, any instruction used to address memory may be used to address the peripherals. The formats of the instruction groups that reference memory are shown below.

| 7, , , 3 | 2 | 1,0 | 7, , , , , , , 0 |                                                                      |

|----------|---|-----|------------------|----------------------------------------------------------------------|

| opcode   | m | ptr | <br>disp         | Memory Reference Instructions                                        |

| opcode   |   | ptr |                  | Memory Increment/Decrement<br>Instructions and Transfer Instructions |

Memory-reference instructions use the PC-relative, indexed, or auto-indexed methods of addressing memory. The memory-increment/decrement instructions and the transfer instructions use the PC-relative or indexed methods of addressing.

The various methods of addressing memory and peripherals are shown below.

Immediate addressing is an addressing format specific to the immediate instruction group.

| Type of      | Operand Formats |            |              |  |  |

|--------------|-----------------|------------|--------------|--|--|

| Addressing   | m               | ptr        | disp         |  |  |

| PC-relative  | 0               | 0          | -128 to +127 |  |  |

| Indexed      | 0               | 1, 2, or 3 | -128 to +127 |  |  |

| Immediate    | 1               | 0          | -128 to +127 |  |  |

| Auto-indexed | 1               | 1, 2, or 3 | -128 to +127 |  |  |

For PC-relative, indexed, and auto-indexed memoryreference instructions, another feature of the addressing architecture is that the contents of the extension register are substituted for the displacement if the instruction displacement equals -128 (-X'80).

#### NOTE:

All arithmetic operations associated with address formation affect only the 12 low-order address bits; no carry is provided to the 4 high-order bits. For systems employing memories of 4k or less, the high-order bits can be ignored as they are set to 0000 following initialization. For systems employing larger memories, the high-order bits must be set to the starting address of the desired 4k block of memory. For example:

00012 enables memory locations  $100016 - 1FFF_{16}$  to be addressed.

$0010_2$  enables memory locations  $2000_{16} - 2FFF_{16}$  to be addressed and so forth.

**PC-Relative Addressing** – A PC-relative address is formed by adding the displacement value specified in the operand field of the instruction to the current contents of the program counter. The displacement is an 8-bit twos-

National Semiconductor

MICROPROCESSOR

complement number, so the range of the PC-relative addressing format is -12810 to +12710 locations from the current contents of the program counter.

Immediate Addressing - Immediate addressing uses the value in the second byte of a double-byte instruction as the operand for the operation to be performed (see below)

For example, compare a Load (LD) instruction to a Load Immediate (LDI) instruction. The Load instruction uses the contents of the second byte of the instruction in computing the effective address of the data to be loaded. The Load Immediate instruction uses the contents of the second byte as the data to be loaded.

Indexed Addressing - Indexed addressing enables the programmer to address any location in memory through the use of the pointer register and the displacement. When indexed addressing is specified in an instruction, the contents of the designated pointer register are added to the displacement to form the effective address. The contents of the pointer register are not modified by indexed addressing.

Auto-Indexed Addressing - Auto-indexed addressing provides the same capabilities as indexed addressing along with the ability to increment or decrement the

designated pointer register by the value of the displacement. If the displacement is less than zero, the pointer register is decremented by the displacement before the contents of the effective address are fetched or stored. If the displacement is equal to or greater than zero, the pointer register is used as the effective address, and the pointer register is incremented by the displacement after the contents of the effective address are fetched or stored

## system implementation

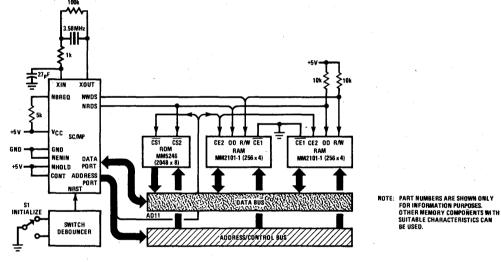

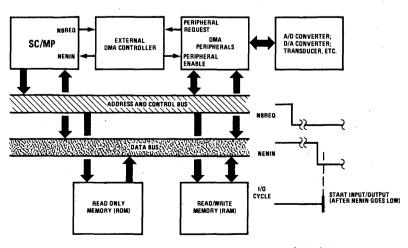

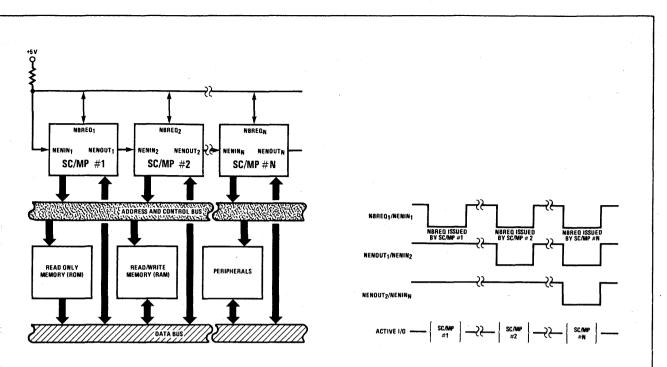

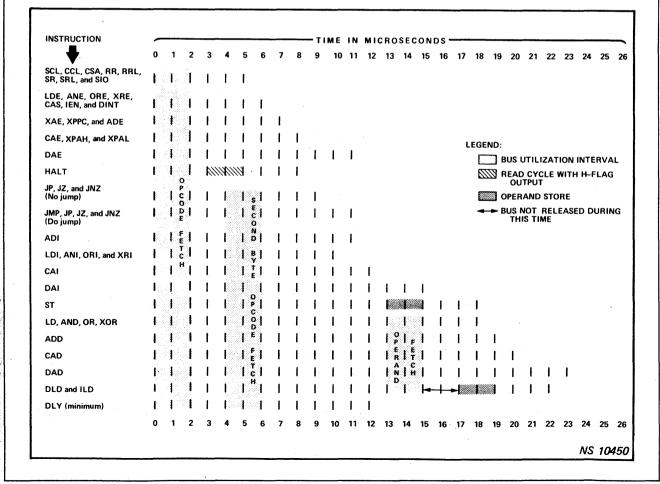

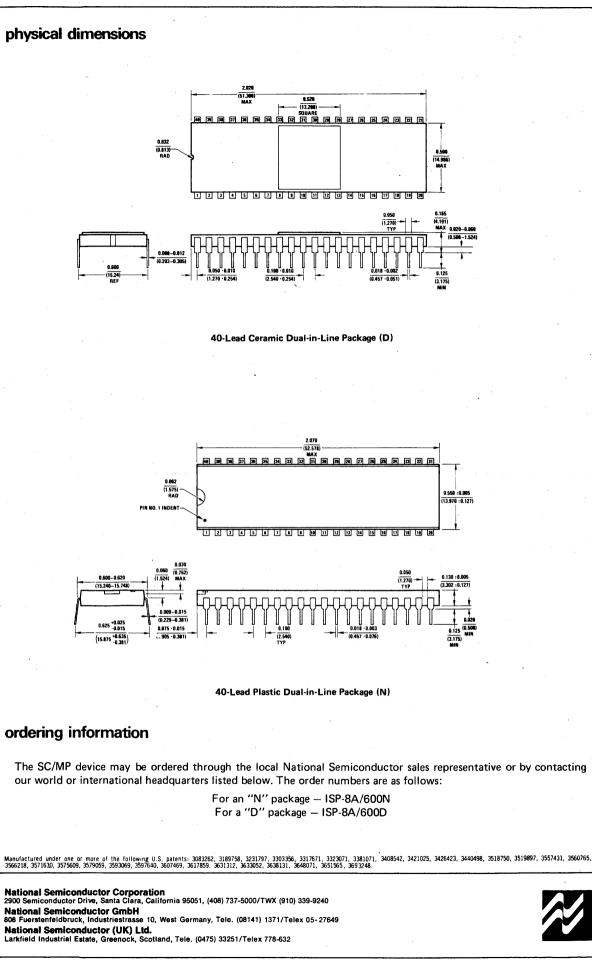

Figures 10 through 12 illustrate typical SC/MP system configurations. In figure 10, SC/MP is shown interconnected to three memory devices to form a stand-alone 4-device system that provides 256 words of read/write memory and 2,048 words for program storage. Figure 11 shows SC/MP interconnected to an external controller for Direct Memory Access (DMA) operation, and figure 12 illustrates a multiprocessor application using SC/MP's built-in logic to control bus access.

FIGURE 10. SC/MP-II Four-Chip System

FIGURE 11. SC/MP-II Interconnected for Direct Memory Access (DMA) Operation

BE USED

TABLE 2. Bus Utilization of Each Instruction

National Semiconductor

MICHOPHOCESSOR

1708

©IC MASTER 1978

| MNEMONIC | DESCRIPTION                             | OBJECT FORMAT      | OPERATION                                                    | MICRO-<br>CYCLES |

|----------|-----------------------------------------|--------------------|--------------------------------------------------------------|------------------|

|          | Memory Reference Instructions           | 7654321076543210   |                                                              |                  |

| LD       | Load                                    | 11000mptr disp     | (AC)←(EA)                                                    | 18               |

| ST       | Store                                   | 11001              | (EA)←(AC)                                                    | 18               |

| AND      | AND                                     | 11010              | (AC)←(AC) ∧ (EA)                                             | 18               |

| OR       | OR                                      | 11011              | (AC)←(AC) ∨ (EA)                                             | 18               |

| XOR-     | Exclusive-OR                            | 11100              | (AC)←(AC) <del>\/</del> (EA)                                 | 18               |

| DAD      | Decimal Add                             | 11101              | (AC)←(AC) <sub>10</sub> + (EA) <sub>10</sub> + (CY/L);(CY/L) | 23               |

| ADD      | Add                                     | 11110              | (AC)←(AC) + (EA) + (CY/L),(CY/L),(OV)                        | 19               |

| CAD      | Complement and Add                      | 11111              | (AC)←(AC) + ~(EA) + (CY/L);(CY/L),(OV)                       | 20               |

|          | Memory Increment/Decrement Instructions | 765432 10 76543210 |                                                              |                  |

| ILD      | Increment and Load                      | 101010ptr disp     | (AC), (EA)←(EA) + 1                                          | 22               |

| DLD      | Decrement and Load                      | 101110             | (AC), (EA)←(EA) – 1                                          | 22               |

|          | Immediate Instructions                  | 76543210 76543210  |                                                              |                  |

| LDI      | Load Immediate                          | 11000100 data      | (AC)← data                                                   | 10               |

| ANI      | AND Immediate                           | 11010100           | (AC)←(AC) ∧ data                                             | 10               |

| ORI      | OR Immediate                            | 11011100           | (AC)←(AC) ∨ data                                             | 10               |

| XRI      | Exclusive-OR Immediate                  | 11100100           | (AC)←(AC) <del>\/</del> data                                 | 10               |

| DAI      | Decimal Add Immediate                   | 11101100           | (AC)←(AC) <sub>10</sub> + data <sub>10</sub> + (CY/L);(CY/L) | 15               |

| ADI      | Add Immediate                           | 11110100           | (AC)←(AC) + data + (CY/L);(CY/L),(OV)                        | .11              |

| CAI      | Complement and Add Immediate            | 1111100            | $(AC) \leftarrow (AC) + \sim data + (CY/L); (CY/L), (OV)$    | 12               |

|          | Transfer Instructions                   | 765432 10 76543210 |                                                              |                  |

| JMP      | Jump                                    | 100100 ptr disp    | (PC)←EA                                                      | 11               |

| JP       | Jump if Positive                        | 100101             | If (AC) ≥ 0, (PC)←EA                                         | 9, 11            |

| JZ       | Jump if Zero                            | 100110             | If (AC) = 0, (PC)←EA                                         | 9, 11            |

| JNZ      | Jump if Not Zero                        | 100111             | If (AC) ≠ 0, (PC)←EA                                         | 9, 11            |

|          | Double-Byte Miscellaneous Instructions  | 7654321076543210   |                                                              |                  |

| DLY      | Delay                                   | 10001111 disp      | count AC to -1,                                              | 13 to            |

|          |                                         |                    | delay = 13 + 2 (AC) + 2 disp + 2 <sup>9</sup> disp           | 131,593          |

|          |                                         |                    | microcycles                                                  |                  |

## SINGLE-BYTE INSTRUCTIONS

| MNEMONIC | DESCRIPTION                            | OBJECT FORMAT | OPERATION                                                                          | MICRO-<br>CYCLES |  |

|----------|----------------------------------------|---------------|------------------------------------------------------------------------------------|------------------|--|

|          | Extension Register Instructions        | 76543210      |                                                                                    |                  |  |

| LDE      | Load AC from Extension                 | 0100000       | (AC)←(E)                                                                           | 6                |  |

| XAE      | Exchange AC and Extension              | 0000001       | (AC)↔(E)                                                                           | 7                |  |

| ANE      | AND Extension                          | 01010000      | (AC)←(AC) ∧ (E)                                                                    | 6                |  |

| ORE      | OR Extension                           | 01011000      | (AC)←(AC) ∨ (E)                                                                    | 6                |  |

| XRE      | Exclusive-OR Extension                 | 01100000      | (AC)←(AC) <del>\/</del> (E)                                                        | 6                |  |

| DAE      | Decimal Add Extension                  | 01101000      | (AC)⊷(AC) <sub>10</sub> + (E) <sub>10</sub> + (CY/L);(CY/L)                        | 11               |  |

| ADE      | Add Extension                          | 01110000      | (AC)←(AC) + (E) + (CY/L);(CY/L),(OV)                                               | 7                |  |

| CAE      | Complement and Add Extension           | 01111000      | $(AC)$ $\leftarrow$ $(AC) + \sim$ $(E) + (CY/L); (CY/L), (OV)$                     | 8                |  |

|          | Pointer Register Move Instructions     | 76543210      |                                                                                    |                  |  |

| XPAL     | Exchange Pointer Low                   | 001100ptr     | (AC)↔(PTR <sub>7:0</sub> )                                                         | 8                |  |

| ХРАН     | Exchange Pointer High                  | 001101        | (AC)↔(PTR <sub>15:8</sub> )                                                        | 8                |  |

| XPPC '   | Exchange Pointer with PC               | 001111        | (PC)↔(PTR)                                                                         | 7                |  |

|          | Shift, Rotate, Serial I/O Instructions | 76543210      |                                                                                    |                  |  |

| SIO      | Serial Input/Output                    | 00011001      | $(E_i) \rightarrow (E_{i-1})$ , SIN $\rightarrow (E_7)$ , $(E_0) \rightarrow SOUT$ | 5                |  |

| SR       | Shift Right                            | 00011100      | $(AC_i) \rightarrow (AC_{i-1}), 0 \rightarrow (AC_7)$                              | · 5              |  |

| SRL      | Shift Right with Link                  | 00011101      | (AC <sub>i</sub> )→(AC <sub>i-1</sub> ), (CY/L)→(AC <sub>7</sub> )                 | 5                |  |

| RR       | Rotate Right                           | 00011110      | $(AC_i) \rightarrow (AC_{i-1}), (AC_0) \rightarrow (AC_7)$                         | 5                |  |

| RRL      | Rotate Right with Link                 | 00011111      | $(AC_i) \rightarrow (AC_{i-1}), (AC_0) \rightarrow (CY/L) \rightarrow (AC_7)$      | 5                |  |

|          | Single-Byte Miscellaneous Instructions | 76543210      |                                                                                    |                  |  |

| HALT     | Halt                                   | 0000000       | Pulse H-flag                                                                       | 8                |  |

| CCL      | Clear Carry/Link                       | 0000010       | (CY/L)←0                                                                           | 5                |  |

| SCL      | Set Carry/Link                         | 00000011      | (CY/L)←1                                                                           | 5                |  |

| DINT     | Disable Interrupt                      | 00000100      | (IE) <del>~</del> 0                                                                | 6                |  |

| IEN 1    | Enable Interrupt                       | 00000101      | (IE)←1                                                                             | 6                |  |

| CSA      | Copy Status to AC                      | 00000110      | (AC)←(SR)                                                                          | 5                |  |

| CAS      | Copy AC to Status                      | 00000111      | (SR)←(AC)                                                                          | 6                |  |

| NOP      | No Operation                           | 00001000      | None                                                                               | 5                |  |

National Semiconductor

MICROPROCESSOR

©IC MASTER 1978

;

| TABLE 4. Instruction Execution Time |                |                 |                      |             |                |                 |                |  |

|-------------------------------------|----------------|-----------------|----------------------|-------------|----------------|-----------------|----------------|--|

| INSTRUCTION                         | READ<br>CYCLES | WRITE<br>CYCLES | TOTAL<br>MICROCYCLES | INSTRUCTION | READ<br>CYCLES | WRITE<br>CYCLES | MICROCYCLES    |  |

| ADD                                 | 3              | 0               | 19                   | JP          | 2              | 0               | 9, 11 for Jump |  |

| ADE                                 | 1              | 0               | 7                    | JZ          | 2              | 0               | 9, 11 for Jump |  |

| ADI                                 | 2              | 0               | 11                   | LD          | 3              | 0               | 18             |  |

| AND                                 | 3              | 0               | 18                   | LDE         | 1              | · 0             | 6              |  |

| ANE                                 | 1              | 0               | 6                    | LDI         | 2              | 0               | 10             |  |